Electronics & Communication Gate Yearwise

Electronics and Communication Gate 2020 Questions with Answer

Ques 14 GATE 2020

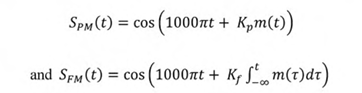

Spm(t) and SFM(t) as defined below, are the phase modulated and the frequency modulated waveforms, respectively, corresponding to the message signal m(t) shown in the figure.

Ques 15 GATE 2020

In a digital communication system, a symbol S randomly chosen from the set {s₁,s₂,s₃,s₄} is transmitted. It is given that s₁=-3, s₂=-1, s₃=+1 and s₄=+2. The received symbol is Y=S+W, where W is a zero-mean unit-variance Gaussian random variable and is independent of S. Pi is the conditional probability of symbol error for the maximum likelihood (ML) decoding when the transmitted symbol S=si. The index i for which the conditional symbol error probability Pi is the highest is

Ques 16 GATE 2020

X is a random variable with uniform probability density function in the interval [-2, 10]. For Y=2X-6, the conditional probability P(Y≤7|X≥5) (rounded off to three decimal places) is

Ques 17 GATE 2020

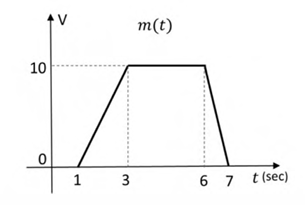

The pole-zero map of a rational function G(s) is shown below. When the closed contour Γ is mapped into the G(s) -plane, then the mapping encircles

Ques 18 GATE 2020

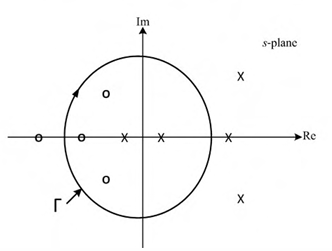

The loop transfer function of a negative feedback system is

Ques 19 GATE 2020

The characteristic equation of a system is

s³+3s²+(K+2)s+3K=0.

In the root locus plot for the given system, as K varies from 0 to ∞, the break-away or break-in point(s) lie within

Ques 20 GATE 2020

A system with transfer function G(s)=1/((s+1)(s+a)), a>0 is subjected to an input 5cos 3t. The steady state output of the system is 1/√10 cos(3t-1.892). The value of a is _______ (rounded off to two decimal places).

Ques 21 GATE 2020

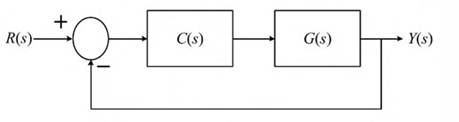

Consider the following closed loop control system

If the steady state error for a unit ramp input is 0.1, then the value of K is

Ques 22 GATE 2020

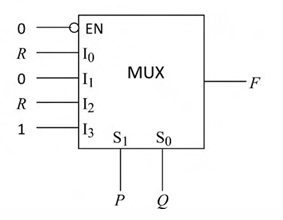

The figure below shows a multiplexer where S₁ and S₀ are the select lines, I₀ to I₃ are the input data lines, EN is the enable line, and F(P,Q,R) is the output. F is

Ques 23 GATE 2020

In an 8085 microprocessor, the number of address lines required to access a 16 K byte memory bank is _________.

Ques 24 GATE 2020

A 10-bit D/A converter is calibrated over the full range from 0 to 10 V. If the input to the D/A converter is 13A (in hex), the output (rounded off to three decimal places) is _______ V.

Ques 25 GATE 2020

P, Q, and R are the decimal integers corresponding to the 4-bit binary number 1100 considered in signed magnitude, 1's complement, and 2's complement representations, respectively. The 6-bit 2's complement representation of (P+Q+R) is

Ques 26 GATE 2020

The state diagram of a sequence detector is shown below. State S₀ is the initial state of the sequence detector. If the output is 1, then

Total Unique Visitors