CS/IT Gate Yearwise

CS/IT Gate 2026 (Set 2)

CS/IT Gate 2025 (Set 1)

CS/IT Gate 2025 (Set 2)

CS/IT Gate 2024 (Set 1)

CS/IT Gate 2024 (Set 2)

CS/IT Gate 2023

CS/IT Gate 2022

CS/IT Gate 2021 (Set 1)

CS/IT Gate 2021 (Set 2)

CS/IT Gate 2020

CS/IT Gate 2019

CS/IT Gate 2018

CS/IT Gate 2017 (Set 1)

CS/IT Gate 2017 (Set 2)

CS/IT Gate 2016 (Set 1)

CS/IT Gate 2016 (Set 2)

CS/IT Gate 2015 (Set 1)

CS/IT Gate 2015 (Set 2)

CS/IT Gate 2015 (Set 3)

CS/IT Gate 2014 (Set 1)

CS/IT Gate 2014 (Set 2)

CS/IT Gate 2014 (Set 3)

CS and IT Gate 2025 Set-1 Questions with Answer

Ques 14 GATE 2025 SET-1

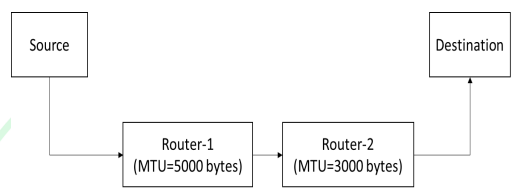

Suppose a message of size 15000 bytes is transmitted from a source to a destination using IPv4 protocol via two routers as shown in the figure. Each router has a defined maximum transmission unit (MTU) as shown in the figure, including IP header. The number of fragments that will be delivered to the destination is ______ (Answer in integer)

IP header = 20 bytes. Original message = 15000 bytes total, so data payload = 14980 bytes.

At Router-1 (MTU = 5000 bytes):

Max data per fragment = 5000 - 20 = 4980 bytes. Rounded down to nearest multiple of 8 = 4976 bytes.

Fragments created: 4976 + 4976 + 4976 + 52 = 14980 bytes → 4 fragments

At Router-2 (MTU = 3000 bytes):

Max data per fragment = 3000 - 20 = 2980. Rounded down to multiple of 8 = 2976 bytes.

Each of the three 4976-byte fragments is split into 2 (2976 + 2000), and the 52-byte fragment passes through unchanged.

Total = 3 × 2 + 1 = 7 fragments delivered to the destination.

Ques 15 GATE 2025 SET-1

Suppose a program is running on a non-pipelined single processor computer system. The computer is connected to an external device that can interrupt the processor asynchronously. The processor needs to execute the interrupt service routine (ISR) to serve this interrupt. The following steps (not necessarily in order) are taken by the processor when the interrupt arrives:

(i) The processor saves the content of the program counter.

(ii) The program counter is loaded with the start address of the ISR.

(iii) The processor finishes the present instruction.

Which ONE of the following is the CORRECT sequence of steps?

Ques 16 GATE 2025 SET-1

The number -6 can be represented as 1010 in 4-bit 2's complement representation. Which of the following is/are CORRECT 2's complement representation(s) of -6?

Ques 17 GATE 2025 SET-1

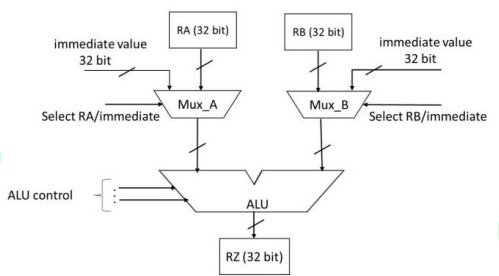

A partial data path of a processor is given in the figure, where RA, RB, and RZ are 32-bit registers. Which option(s) is/are CORRECT related to arithmetic operations using the data path as shown?

Ques 18 GATE 2025 SET-1

Consider a memory system with 1M bytes of main memory and 16K bytes of cache memory. Assume that the processor generates 20-bit memory address, and the cache block size is 16 bytes. If the cache uses direct mapping, how many bits will be required to store all the tag values? [Assume memory is byte addressable, 1K=210, 1M=220.]

Ques 19 GATE 2025 SET-1

A processor has 64 general-purpose registers and 50 distinct instruction types. An instruction is encoded in 32-bits. What is the maximum number of bits that can be used to store the immediate operand for the given instruction?

ADD R1, #25 //R1=R1+25

Ques 20 GATE 2025 SET-1

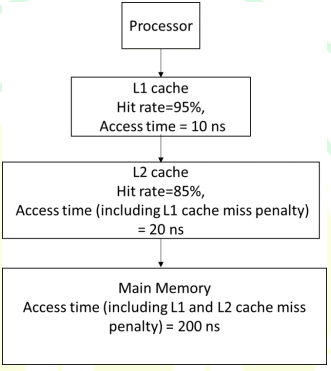

A computer has a memory hierarchy consisting of two-level cache (L1 and L2) and a main memory. If the processor needs to access data from memory, it first looks into L1 cache. If the data is not found in L1 cache, it goes to L2 cache. If it fails to get the data from L2 cache, it goes to main memory, where the data is definitely available. Hit rates and access times of various memory units are shown in the figure. The average memory access time in nanoseconds (ns) is ______ (rounded off to two decimal places)

AMAT = TL1 + (1 - HL1) × [TL2 + (1 - HL2) × TMM]

where TL1, TL2, TMM are the access times of L1, L2, and main memory, and HL1, HL2 are their respective hit rates.

Every memory access always checks L1 first (TL1 is always paid). On an L1 miss, L2 is checked. On an L2 miss, main memory is accessed.

Substituting the values from the given figure into the formula gives an AMAT of approximately 11.85 ns, which falls within the official accepted range of 11.83 to 11.87.

Ques 21 GATE 2025 SET-1

Which of the following statement(s) is/are TRUE for any binary search tree (BST) having n distinct integers?

Statement A: The maximum length of a path from the root node to any other node is (n-1).

Analysis: In a skewed BST (all nodes in a single line), the path from root to the deepest node has (n-1) edges.

Example: BST with nodes 1→2→3→4→5 has maximum path length = 4 = (5-1)

Result: TRUE ✓

Statement B: An inorder traversal will always produce a sorted sequence of elements.

Analysis: By definition of BST, left subtree < root < right subtree. Inorder traversal (Left→Root→Right) always visits nodes in ascending order.

Example: BST with root 5, left child 3, right child 7 gives inorder: 3, 5, 7 (sorted)

Result: TRUE ✓

Statement C: Finding an element takes O(log₂n) time in the worst case.

Analysis: In the worst case, BST becomes skewed (like a linked list) and finding an element takes O(n) time, not O(log₂n).

O(log₂n) is only for balanced BST, not for any BST.

Result: FALSE ✗

Statement D: Every BST is also a Min-Heap.

Analysis: Min-Heap property: parent < both children (for all nodes).

BST property: left child < parent < right child.

In BST, the right child can be greater than parent, violating Min-Heap property.

Example: BST with root 5, left child 3, right child 7. Here 7 > 5, so not a Min-Heap.

Result: FALSE ✗

Answer: A and B are TRUE

Ques 22 GATE 2025 SET-1

The height of any rooted tree is defined as the maximum number of edges in the path from the root node to any leaf node.

Suppose a Min-Heap T stores 32 keys. The height of T is ______ (Answer in integer)

Given: Min-Heap with 32 keys

Min-Heap structure:

A Min-Heap is a complete binary tree where every node is smaller than its children.

Formula for height of complete binary tree

For a complete binary tree with n nodes:

Height (h) = ⌊log₂(n)⌋

where ⌊ ⌋ means floor function (round down)

Calculating the height

Number of nodes (n) = 32

Height = ⌊log₂(32)⌋

Height = ⌊log₂(2⁵)⌋

Height = ⌊5⌋

Height = 5

Verification:

A complete binary tree of height 5 has:

- Minimum nodes = 2⁵ = 32 nodes

- Maximum nodes = 2⁶ - 1 = 63 nodes

Since we have exactly 32 nodes, height = 5

Answer: 5

Ques 23 GATE 2025 SET-1

In a double hashing scheme, h1(k)=k mod 11 and h2(k)=1+(k mod 7) are the auxiliary hash functions. The size m of the hash table is 11. The hash function for the i-th probe in the open address table is [h1(k)+i h2(k)] mod m. The following keys are inserted in the given order: 63, 50, 25, 79, 67, 24.

The slot at which key 24 gets stored is ______ (Answer in integer)

The correct answer is Slot 10.

Given: h1(k) = k mod 11, h2(k) = 1 + (k mod 7), table size m = 11.

Probe formula: (h1(k) + i × h2(k)) mod 11

First, insert all preceding keys to know which slots are occupied:

63: 63 mod 11 = 8 → Slot 8

50: 50 mod 11 = 6 → Slot 6

25: 25 mod 11 = 3 → Slot 3

79: 79 mod 11 = 2 → Slot 2

67: 67 mod 11 = 1 → Slot 1

Occupied slots before inserting 24: {1, 2, 3, 6, 8}

Now insert key 24:

h1(24) = 24 mod 11 = 2 → Slot 2 occupied (79)

h2(24) = 1 + (24 mod 7) = 1 + 3 = 4

Probe i=1: (2 + 1×4) mod 11 = 6 → occupied (50)

Probe i=2: (2 + 2×4) mod 11 = 10 mod 11 = 10 → empty ✓

Key 24 is stored at Slot 10.

Ques 24 GATE 2025 SET-1

A schedule of three database transactions T1, T2, and T3 is shown.

Ri(A) and Wi(A) denote read and write of data item A by transaction Ti,i=1,2,3.

The transaction T1 aborts at the end. Which other transaction(s) will be required to be rolled back?

R1(X)W1(Y)R2(X)R2(Y)R3(Y)ABORT(T1)

Ques 25 GATE 2025 SET-1

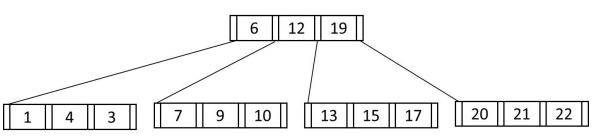

Consider the following B+ tree with 5 nodes, in which a node can store at most 3 key values. The value 23 is now inserted in the B+ tree. Which of the following options(s) is/are CORRECT?

Ques 26 GATE 2025 SET-1

Consider two relations describing teams and players in a sports league:

• teams (tid, tname): tid, tname are team-id and team-name, respectively

• players (pid, pname, tid): pid, pname, and tid denote player-id, player-name and the team-id of the player, respectively

Which ONE of the following tuple relational calculus queries returns the name of the players who play for the team having tname as 'MI'?

Total Unique Visitors