CS/IT Gate Yearwise

CS/IT Gate 2026 (Set 2)

CS/IT Gate 2025 (Set 1)

CS/IT Gate 2025 (Set 2)

CS/IT Gate 2024 (Set 1)

CS/IT Gate 2024 (Set 2)

CS/IT Gate 2023

CS/IT Gate 2022

CS/IT Gate 2021 (Set 1)

CS/IT Gate 2021 (Set 2)

CS/IT Gate 2020

CS/IT Gate 2019

CS/IT Gate 2018

CS/IT Gate 2017 (Set 1)

CS/IT Gate 2017 (Set 2)

CS/IT Gate 2016 (Set 1)

CS/IT Gate 2016 (Set 2)

CS/IT Gate 2015 (Set 1)

CS/IT Gate 2015 (Set 2)

CS/IT Gate 2015 (Set 3)

CS/IT Gate 2014 (Set 1)

CS/IT Gate 2014 (Set 2)

CS/IT Gate 2014 (Set 3)

CS and IT Gate 2024 Set-2 Questions with Answer

Ques 40 GATE 2024 Set-2

A processor with 16 general purpose registers uses a 32-bit instruction format. The instruction format consists of an opcode field, an addressing mode field, two register operand fields, and a 16-bit scalar field. If 8 addressing modes are to be supported, the maximum number of unique opcodes possible for every addressing mode is __________.

Ques 41 GATE 2024 Set-2

A non-pipelined instruction execution unit operating at 2 GHz takes an average of 6 cycles to execute an instruction of a program P. The unit is then redesigned to operate on a 5-stage pipeline at 2 GHz. Assume that the ideal throughput of the pipelined unit is 1 instruction per cycle. In the execution of program P, 20% instructions incur an average of 2 cycles stall due to data hazards and 20% instructions incur an average of 3 cycles stall due to control hazards. The speedup (rounded off to one decimal place) obtained by the pipelined design over the non-pipelined design is ___________.

Ques 42 GATE 2024 Set-2

Let L1 be the language represented by the regular expression b*ab*(ab*ab*)* and L2 = {w ∈ (a + b)* | |w| ≤ 4}, where |w| denotes the length of string w. The number of strings in L2 which are also in L1 is ___________.

Ques 43 GATE 2024 Set-2

Let Zn be the group of integers {0,1,2,...,n-1} with addition modulo n as the group operation. The number of elements in the group Z2 x Z3 x Z4 that are their own inverses is

Ques 44 GATE 2024 Set-2

Consider a 32-bit system with 4 KB page size and page table entries of size 4 bytes each. Assume 1 KB = 210 bytes. The OS uses a 2-level page table for memory management, with the page table containing an outer page directory and an inner page table. The OS allocates a page for the outer page directory upon process creation. The OS uses demand paging when allocating memory for the inner page table, i.e., a page of the inner page table is allocated only if it contains at least one valid page table entry.

An active process in this system accesses 2000 unique pages during its execution, and none of the pages are swapped out to disk. After it completes the page accesses, let X denote the minimum and Y denote the maximum number of pages across the two levels of the page table of the process. The value of X + Y is ________.

Ques 45 GATE 2024 Set-2

Consider the following augmented grammar, which is to be parsed with a SLR parser. The set of terminals is {a,b,c,d,#,&}.

S' → S

S → SS | Aa | bAc | Bc | bBa

𝐴 → 𝑑#

𝐵 → @

Let I0 = CLOSURE({S' → •S}) The number of items in the set GOTO(I0, S) is

Ques 46 Gate 2024 Set-2

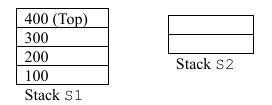

Let S1 and S2 be two stacks. S1 has capacity of 4 elements. S2 has capacity of

2 elements. S1 already has 4 elements: 100, 200, 300, and 400, whereas S2 is

empty, as shown below.

PushToS2: Pop the top element from S1 and push it on S2.

PushToS1: Pop the top element from S2 and push it on S1.

GenerateOutput: Pop the top element from S1 and output it to the user.

Note that the pop operation is not allowed on an empty stack and the push operation is not allowed on a full stack.

Which of the following output sequences can be generated by using the above operations?

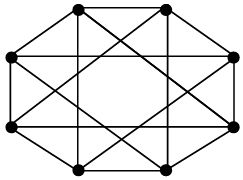

Ques 47 Gate 2024 Set-2

The chromatic number of a graph is the minimum number of colours used in a proper colouring of the graph. The chromatic number of the following graph is _________

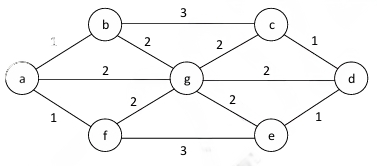

Ques 48 Gate 2024 Set-2

The number of distinct minimum-weight spanning trees of the following graph is _________

Ques 49 Gate 2024 Set-2

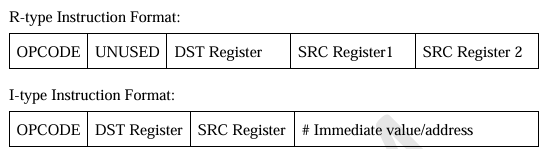

A processor uses a 32-bit instruction format and supports byte-addressable memory

access. The ISA of the processor has 150 distinct instructions. The instructions are

equally divided into two types, namely R-type and I-type, whose formats are shown

below.

R-type Instruction Format:

Let 𝑋 be the number of bits used to encode the UNUSED field, 𝑌 be the number of bits used to encode the OPCODE field, and 𝑍 be the number of bits used to encode the immediate value/address field. The value of 𝑋 + 2𝑌 + 𝑍 is ________

Ques 50 Gate 2024 Set-2

Consider 4-variable functions f1, f2, f3, f4 expressed in sum-of-minterms form as given below.

f1 = ∑(0,2,3,5,7,8,11,13)

f2 = ∑(1,3,5,7,11,13,15)

f3 = ∑(0,1,4,11)

f4 = ∑(0,2,6,13)

Ques 51 Gate 2024 Set-2

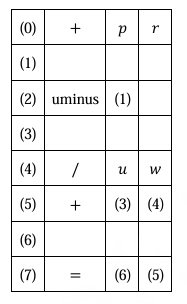

Consider the following expression: 𝑥[𝑖]=(𝑝+𝑟)∗−𝑠[𝑖]+𝑢/𝑤. The following sequence shows the list of triples representing the given expression, with entries missing for triples (1), (3), and (6).

Ques 52 Gate 2024 Set-2

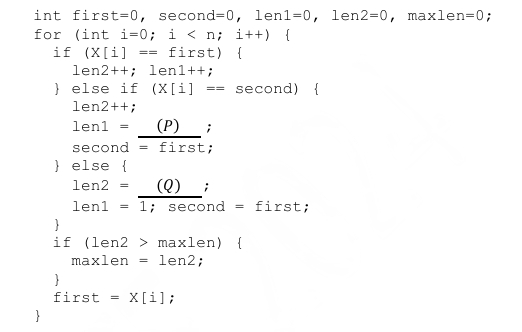

Consider an array X that contains n positive integers. A subarray of X is defined to be a sequence of array locations with consecutive indices. The C code snippet given below has been written to compute the length of the longest subarray of X that contains at most two distinct integers. The code has two missing expressions labelled (𝑃)and (𝑄).

(Hint: At the end of the i-th iteration, the value of len1 is the length of the longest subarray ending with X[i] that contains all equal values, and len2 is the length of the longest subarray ending with X[i] that contains at most two distinct values.)

Total Unique Visitors