CS/IT Gate Yearwise

CS/IT Gate 2026 (Set 2)

CS/IT Gate 2025 (Set 1)

CS/IT Gate 2025 (Set 2)

CS/IT Gate 2024 (Set 1)

CS/IT Gate 2024 (Set 2)

CS/IT Gate 2023

CS/IT Gate 2022

CS/IT Gate 2021 (Set 1)

CS/IT Gate 2021 (Set 2)

CS/IT Gate 2020

CS/IT Gate 2019

CS/IT Gate 2018

CS/IT Gate 2017 (Set 1)

CS/IT Gate 2017 (Set 2)

CS/IT Gate 2016 (Set 1)

CS/IT Gate 2016 (Set 2)

CS/IT Gate 2015 (Set 1)

CS/IT Gate 2015 (Set 2)

CS/IT Gate 2015 (Set 3)

CS/IT Gate 2014 (Set 1)

CS/IT Gate 2014 (Set 2)

CS/IT Gate 2014 (Set 3)

CS and IT Gate 2015 Set-2 Questions with Answer

Ques 14 Gate 2015 Set-2

A link has a transmission speed of 106 bits/sec. It uses data packets of size 1000 bytes each. Assume that the acknowledgment has negligible transmission delay, and that its propagation delay is the same as the data propagation delay. Also assume that the processing delays at nodes are negligible. The efficiency of the stop-and-wait protocol in this setup is exactly 25%. The value of the one-way propagation delay (in milliseconds) is ___________.

Ques 15 Gate 2015 Set-2

Which one of the following statements is NOT correct about HTTP cookies?

Ques 16 GATE 2015 SET-2

Assume that for a certain processor, a read request takes 50 nanoseconds on a cache miss and 5 nanoseconds on a cache hit. Suppose while running a program, it was observed that 80% of the processor's read requests result in a cache hit. The average read access time in nanoseconds is _______.

Ques 17 GATE 2015 SET-2

A computer system implements a 40-bit virtual address, page size of 8 kilobytes, and a 128-entry translation look-aside buffer (TLB) organized into 32 sets each having four ways. Assume that the TLB tag does not store any process id. The minimum length of the TLB tag in bits is _______.

Ques 18 GATE 2015 SET-2

A computer system implements 8 kilobyte pages and a 32-bit physical address space. Each page table entry contains a valid bit, a dirty bit, three permission bits, and the translation. If the maximum size of the page table of a process is 24 megabytes, the length of the virtual address supported by the system is _______ bits.

Ques 19 GATE 2015 SET-2

Consider the sequence of machine instructions given below:

MUL R5, R0, R1

DIV R6, R2, R3

ADD R7, R5, R6

SUB R8, R7, R4

In the above sequence, R0 to R8 are general purpose registers. In the instructions shown, the first register stores the result of the operation performed on the second and the third registers. This sequence of instructions is to be executed in a pipelined instruction processor with the following 4 stages: (1) Instruction Fetch and Decode (IF), (2) Operand Fetch (OF), (3) Perform Operation (PO) and (4) Write back the result (WB). The IF, OF and WB stages take 1 clock cycle each for any instruction. The PO stage takes 1 clock cycle for ADD or SUB instruction, 3 clock cycles for MUL instruction and 5 clock cycles for DIV instruction. The pipelined processor uses operand forwarding from the PO stage to the OF stage. The number of clock cycles taken for the execution of the above sequence of instructions is _______.

Ques 20 GATE 2015 SET-2

Consider a processor with byte-addressable memory. Assume that all registers, including Program Counter (PC) and Program Status Word (PSW), are of size 2 bytes. A stack in the main memory is implemented from memory location (0100)16 and it grows upward. The stack pointer (SP) points to the top element of the stack. The current value of SP is (016E)16. The CALL instruction is of two words, the first word is the op-code and the second word is the starting address of the subroutine (one word = 2 bytes). The CALL instruction is implemented as follows:

•Store the current value of PC in the stack.

•Store the value of PSW register in the stack.

•Load the starting address of the subroutine in PC.

The content of PC just before the fetch of a CALL instruction is (5FA0)16. After execution of the CALL instruction, the value of the stack pointer is

Ques 21 Gate 2015 Set-2

A binary tree T has 20 leaves. The number of nodes in T having two children is ________

Ques 22 Gate 2015 Set-2

Consider a complete binary tree where the left and the right subtrees of the root are max-heaps. The lower bound for the number of operations to convert the tree to a heap is

Ques 23 GATE 2015 SET-2

An unordered list contains n distinct elements. The number of comparisons to find an element in this list that is neither maximum nor minimum is

Ques 24 GATE 2015 SET-2

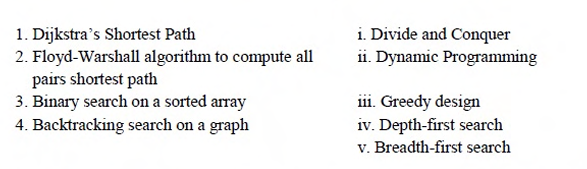

Given below are some algorithms, and some algorithm design paradigms.

Ques 25 GATE 2015 SET-2

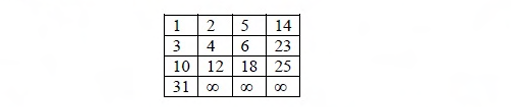

A Young tableau is a 2D array of integers increasing from left to right and from top to bottom. Any unfilled entries are marked with ∞, and hence there cannot be any entry to the right of, or below a ∞. The following Young tableau consists of unique entries.

Ques 26 GATE 2015 SET-2

Which one of the following hash functions on integers will distribute keys most uniformly over 10 buckets numbered 0 to 9 for i ranging from 0 to 2020?

Total Unique Visitors