Electrical Engineering > GATE 2025 > Controller Design

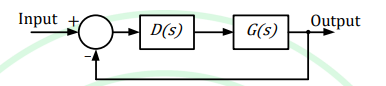

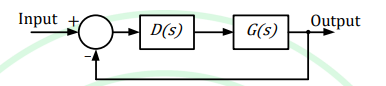

A controller D(s) of the form (1+KDs) is to be designed for the plant G(s)=1000√2/(s(s+10)2) as shown in the figure.

The value of KD that yields a phase margin of 45° at the gain cross-over frequency of 10 rad/sec is ______ (round off to one decimal place).

The value of KD that yields a phase margin of 45° at the gain cross-over frequency of 10 rad/sec is ______ (round off to one decimal place).

Explanation

Correct : 0.1

Similar Questions

What is the worst-case time complexity of insertion in an AVL tree?

Which operations on a binary search tree have O(h) complexity?

Compare search complexities of sorted array vs balanced BST.