Electrical Engineering > GATE 2013 SET-1 > Logic Circuits

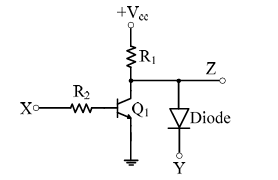

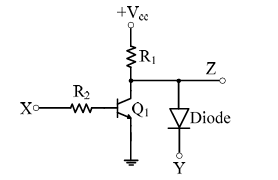

In the circuit shown below, Q1 has negligible collector-to-emitter saturation voltage and the diode drops negligible voltage across it under forward bias. If V<sub>cc</sub> is +5 V, X and Y are digital signals with 0 V as logic 0 and Vcc as logic 1, then the Boolean expression for Z is

Correct :

Similar Questions

As you grow older, an injury to your _________ may take longer to _________.

In a 500 m race, P and Q have speeds in the ratio of 3 ∶ 4. Q starts the race when P has already covered 140 m.

What is the distance between P and Q (in m) whe...

Three bells P, Q, and R are rung periodically in a school. P is rung every 20 minutes; Q is rung every 30 minutes and R is rung every 50 minutes. If all the thr...

Total Unique Visitors

Loading......