When program P is executed, the number of clock cycles for which the pipeline is stalled due to structural hazards in the EX stage is ______. (answer in integer)

Correct : 95

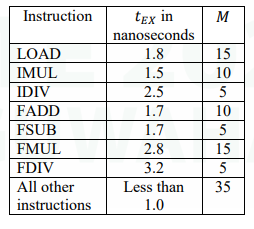

To find the total number of stall cycles caused by structural hazards in the EX stage, we need to determine how many clock cycles each instruction spends occupying that stage.

1. Understanding Stall Cycles

The pipeline clock cycle duration is 1 nanosecond (ns). Because execution must happen in discrete clock cycles, if an instruction''s execution time (tEX) is not an exact integer, it will occupy the EX stage for the ceiling of its tEX (i.e., ceil(tEX) cycles).

In an ideal pipeline, an instruction leaves the stage after exactly 1 cycle to let the next instruction enter. If an instruction stays for C cycles, it blocks the pipeline, causing C - 1 stall cycles.

2. Calculating Stalls per Instruction Type

Using the formula Stalls = ceil(tEX) - 1, let''s look at each instruction type:

- LOAD: tEX = 1.8 ns → ceil(1.8) = 2 cycles. Stalls = 2 - 1 = 1

- IMUL: tEX = 1.5 ns → ceil(1.5) = 2 cycles. Stalls = 2 - 1 = 1

- IDIV: tEX = 2.5 ns → ceil(2.5) = 3 cycles. Stalls = 3 - 1 = 2

- FADD: tEX = 1.7 ns → ceil(1.7) = 2 cycles. Stalls = 2 - 1 = 1

- FSUB: tEX = 1.7 ns → ceil(1.7) = 2 cycles. Stalls = 2 - 1 = 1

- FMUL: tEX = 2.8 ns → ceil(2.8) = 3 cycles. Stalls = 3 - 1 = 2

- FDIV: tEX = 3.2 ns → ceil(3.2) = 4 cycles. Stalls = 4 - 1 = 3

- Other: tEX < 1.0 ns → ceil(<1.0) = 1 cycle. Stalls = 1 - 1 = 0

3. Total Stall Cycles for Program P

Now we multiply the stall cycles per instruction by its frequency (M) in the sequence of 100 instructions:

- LOAD: 15 × 1 = 15 stalls

- IMUL: 10 × 1 = 10 stalls

- IDIV: 5 × 2 = 10 stalls

- FADD: 10 × 1 = 10 stalls

- FSUB: 5 × 1 = 5 stalls

- FMUL: 15 × 2 = 30 stalls

- FDIV: 5 × 3 = 15 stalls

- Other: 35 × 0 = 0 stalls

Total Stalls = 15 + 10 + 10 + 10 + 5 + 30 + 15 + 0 = 95.

Correct Answer: 95

Similar Questions

Total Unique Visitors