Computer Sciences > GATE 2026 SET-1 > Sequential Circuits

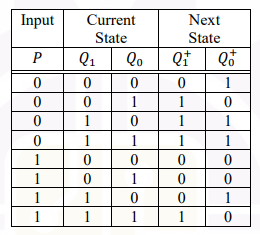

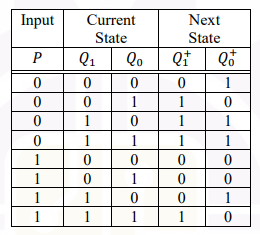

Consider a 2-bit saturating up/down counter that performs the saturating up count when the input P is 0, and the saturating down count when P is 1. The Next State table of the counter is as shown below. The counter is built as a synchronous sequential circuit using D flip-flops.

Which one of the following options corresponds to the expressions for the inputs of the D flip-flops, D1 and D0?

Which one of the following options corresponds to the expressions for the inputs of the D flip-flops, D1 and D0?

Correct : d

Similar Questions

We want to design a synchronous counter that counts the sequence 0-1-0-2-0-3 and then repeats. The minimum number of J-K flip-flops required to implement this c...

Consider a 3-bit counter, designed using T flip-flops, as shown below:

Assuming the initial state of the counter given by PQR as 000, what are the next three...

Consider the given sequential circuit designed using D-Flip-flops. The circuit is initialized with some value (initial state). The number of distinct states the...

Total Unique Visitors

Loading......