Computer Sciences > Gate 2024 Set-2 > Tree

A processor uses a 32-bit instruction format and supports byte-addressable memory

access. The ISA of the processor has 150 distinct instructions. The instructions are

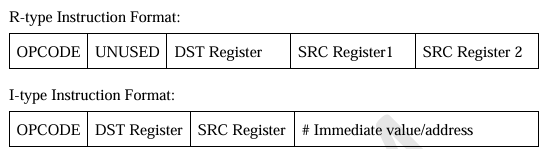

equally divided into two types, namely R-type and I-type, whose formats are shown

below.

R-type Instruction Format:

In the OPCODE, 1 bit is used to distinguish between I-type and R-type instructions

and the remaining bits indicate the operation. The processor has 50 architectural

registers, and all register fields in the instructions are of equal size.

In the OPCODE, 1 bit is used to distinguish between I-type and R-type instructions

and the remaining bits indicate the operation. The processor has 50 architectural

registers, and all register fields in the instructions are of equal size.

Let 𝑋 be the number of bits used to encode the UNUSED field, 𝑌 be the number of bits used to encode the OPCODE field, and 𝑍 be the number of bits used to encode the immediate value/address field. The value of 𝑋 + 2𝑌 + 𝑍 is ________

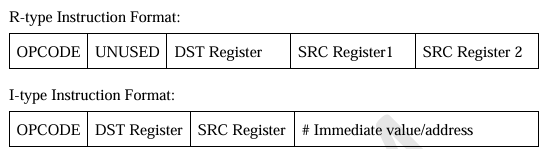

R-type Instruction Format:

Let 𝑋 be the number of bits used to encode the UNUSED field, 𝑌 be the number of bits used to encode the OPCODE field, and 𝑍 be the number of bits used to encode the immediate value/address field. The value of 𝑋 + 2𝑌 + 𝑍 is ________

Correct : a

Similar Questions

The height of a tree is the length of the longest root-to-leaf path in it. The maximum and minimum number of nodes in a binary tree of height 5 are

Let T be a tree with 10 vertices. The sum of the degrees of all the vertices in T is _____.

In a B+ tree, the requirement of at least half-full (50%) node occupancy is relaxed

for which one of the following cases?

Total Unique Visitors

Loading......